LSI活動報告

概要

お客様から回路追加するのにスペースが足りないので回路の一部をLSI化したいという要求を頂きましたが、当社に技術がなくご要望にお応えすることができませんでした。

これをきっかけにLSI(FPGA)の設計技術習得に向けた取り組みの機会を頂きましたので、これまでの活動を報告します。

LSI化のメリット

・回路の小型化

複数の部品で構成された回路を FPGAに集積することで、大幅な小型化ができます。

また、集積することで部品数が減り生産工数の減少、部品の調達・管理が今までよりも簡略化できます。

・回路をプログラム化する

FPGAは好きなタイミングでプログラムの書き換えができるため、機能仕様の異なる基板もプログラムを変更することで仕様ごとに基板を作らずに済み、製品管理が容易になります。

・一貫した対応が可能

FPGAの設計会社は現在も存在しています。

しかしFPGAを組み込んだ回路設計行い、ものづくりまで行えるメーカーは少数だと考えます。

京西ではアートワーク設計も対応できて、生産ラインもあり量産も行えるため大きな強みとなります。

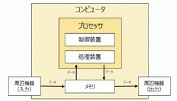

FPGAとは

従来も回路を集約する手法、部品は存在していました。

代表的なLSIは、一度プログラムを書き込むと 変更できません。

対して、FPGAは プログラムの書き換えが容易に出来るので、簡単に回路を変更することができます。

HDLと呼ばれるプログラム言語で組むことにより 様々な回路を構築することができます。

従来のLSI

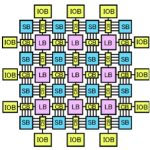

FPGA

IOB/CB:入出力装置とCPUをつなぐ

SB:命令(プログラム)データを記憶する

LB:命令を読み出し解読して実行する

各セルが独立してそれぞれの命令を実行することで任意の回路を構成できる。

本活動の目標

冒頭で紹介した客先要求のタイマー回路小型化を実現することでFPGAの理解を深めていきます。

FPGAの選定

お客様の使用状況と市場シェア調査を実施、評価ボードや開発環境が充実していることも考慮し、Xilinx社のFPGA(評価ボード)を使うこととしました。

要素技術

①分周回路

元の回路では 32.768[kHz]を分周して 1[Hz]を生成する回路ですが、FPGA評価ボードの基準水晶発振器は 100[MHz]なので 100[MHz]から分周して1[Hz]を生成するプログラムとしています。

分周する値は 定数として 基準周波数が変わった場合でも 簡単に変更できるよう構成すします。

②カウンタ回路

元の回路では 12bitカウンタですが、今回はFPGA評価の為 4bitとしました。

但し 12bitへの拡張が容易なように構成します。

③ SW設定読込回路

4個のSWのON/OFFの値を読み込んで記憶する回路です。

基準クロック(10MHz)の立ち上がりでSW設定を読み込んで変数に格納します。

動作が確認出来る様にボード上のLEDでその値を表示させています。

④ 一致検出回路

カウンタ値とSW設定値とが一致したら“Hi”信号を出す回路です。

カウンタ値≧SW設定値の場合したことを示す“Hi”を出します。

一致した時の“Hi”信号はボード上のLEDで表示させています。

⑤ 一致信号出力回路

一致検出回路から出力される信号を一致信号出力に固定する回路です。

一致検出信号は一致条件から外れてしまうと信号が無くなってしまいますが

この回路で一致検出信号を“Hi”に維持します。

【プログラムとデバックの一例:SW設定読込回路】

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////

// Module Name: SETTING

//////////////////////////////////////////////////////////////////////////////

// SETTING SW設定の読み込み

// SW0~3の値を 変数に保存する

module SETTING(

input CLK,

input SW0,

input SW1,

input SW2,

input SW3,

output reg LED0_B,

output reg LED0_R,

output reg LED0_G,

output reg LED1_B,

output reg LED1_R,

output reg LED1_G,

output reg LED2_B,

output reg LED2_R,

output reg LED2_G,

output reg LED3_B,

output reg LED3_R,

output reg LED3_G

);

// SW設定格納用変数

// 一致検出回路でカウンタ値と比較するために変数に格納する

reg [3:0] set1;

always @(posedge CLK)

begin

// SW設定を変数(set1)に読み込む

set1[0] <= SW0;

set1[1] <= SW1;

set1[2] <= SW2;

set1[3] <= SW3;

// SW設定を LED0~3(赤)で表示する

LED0_R <= set1[0];

LED1_R <= set1[1];

LED2_R <= set1[2];

LED3_R <= set1[3];

※DEBUG表示

end

endmodule

現状成果

HDL(Verilog-HDL)言語プログラムの基礎学習とFPGA評価ボード(ARTY_S7)の仕様理解と動作を確認、タイマー回路を機能ごと(分周・カウンタ・SW設定読込・一致検出・一致信号出力)の回路に細分化し、それぞれプログラム作成→評価ボードによるデバックを実施、その後、各回路を結合したタイマー回路全体の動作確認までを評価ボード上で行いました。

FPGA化の効果

まだ動作確認の段階ですが、ここまでで見えてきたFPGA化の効果を検証しました。

回路規模が増えていくと FPGA化の効果は 更に大きくなると考えます。

課題

ソフトウエアのプログラムは Aの処理、Bの処理、Cの処理と順番に処理されますが、HDLのプログラムは Aの処理、Bの処理、Cの処理が 同時に処理されます。

今までの考え方と異なる処理の流れの為、HDLプログラミングの流れを深く理解する必要があります。

今後の取組み

現行回路と同じ動きとなっているか?実基板上で既存の回路と接続しての動作評価実施に向け試作品の製作を進めています。

またプログラム作成以外にも実際にFPGAを作る為には必要な技術がいくつもありますので、その技術習得にも取り組んでいます。

弊社の電源技術はお客様のニーズに合わせたカスタム電源の開発・設計を行っており、高信頼・耐振性・長寿命・特殊環境など、あらゆる各種産業機器分野にて採用実績が御座います。

また、汎用品を用いたユニット電源開発からアプリケーションに合わせた付加機能の設計開発も得意としておりますので、回路・電気から筐体設計に至るまで、高度な設計・製造技術でご要望にお応え致します。